Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

®<br />

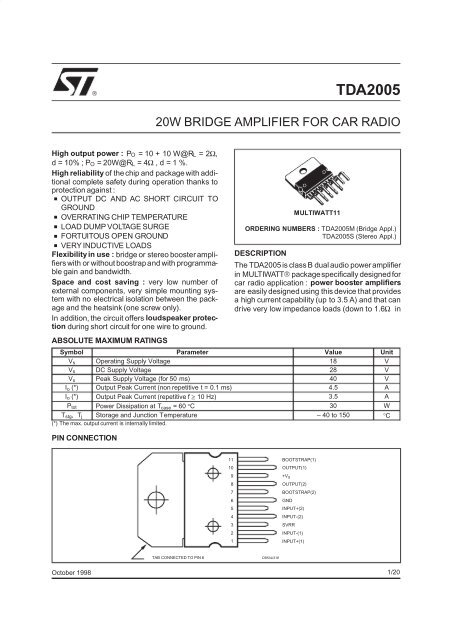

<strong>TDA2005</strong><br />

20W BRIDGE AMPLIFIER FOR CAR RADIO<br />

High output power : PO = 10 + 10 W@RL =2Ω,<br />

d = 10% ; P O = 20W@R L =4Ω,d=1%.<br />

High reliability of the chip and package with additional<br />

.<br />

complete safety during operation thanks to<br />

protection against :<br />

OUTPUT DC AND AC SHORT CIRCUIT TO<br />

GROUND<br />

OVERRATING CHIP TEMPERATURE<br />

.<br />

LOAD DUMP VOLTAGE SURGE<br />

FORTUITOUS OPEN GROUND<br />

VERY INDUCTIVE LOADS<br />

Flexibility in use : bridge or stereo booster amplifiers<br />

with or without boostrapand with programmable<br />

gain and bandwidth.<br />

Space and cost saving : very low number of<br />

external components, very simple mounting system<br />

with no electrical isolation between the package<br />

and the heatsink (one screw only).<br />

In addition, the circuit offers loudspeaker protection<br />

during short circuit for one wire to ground.<br />

ABSOLUTE MAXIMUM RATINGS<br />

PIN CONNECTION<br />

MULTIWATT11<br />

ORDERING NUMBERS : <strong>TDA2005</strong>M (Bridge Appl.)<br />

<strong>TDA2005</strong>S (Stereo Appl.)<br />

DESCRIPTION<br />

The <strong>TDA2005</strong> is class B dual audio power amplifier<br />

in MULTIWATT® packagespecifically designed for<br />

car radio application : power booster amplifiers<br />

are easily designed using this device that provides<br />

a high current capability (up to 3.5 A) and that can<br />

drive very low impedance loads (down to 1.6Ω in<br />

Symbol Parameter Value Unit<br />

V s Operating Supply Voltage 18 V<br />

V s DC Supply Voltage 28 V<br />

V s Peak Supply Voltage (for 50 ms) 40 V<br />

I o (*) Output Peak Current (non repetitive t = 0.1 ms) 4.5 A<br />

I o (*) Output Peak Current (repetitive f ≥ 10 Hz) 3.5 A<br />

P tot Power Dissipation at T case =60°C 30 W<br />

T stg , T j Storage and Junction Temperature – 40 to 150 °C<br />

(*) The max. output current is internally limited.<br />

11<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

BOOTSTRAP(1)<br />

OUTPUT(1)<br />

+V S<br />

OUTPUT(2)<br />

BOOTSTRAP(2)<br />

GND<br />

INPUT+(2)<br />

INPUT-(2)<br />

SVRR<br />

INPUT-(1)<br />

INPUT+(1)<br />

TAB CONNECTED TO PIN 6<br />

D95AU318<br />

October 1998<br />

1/20

<strong>TDA2005</strong><br />

SCHEMATIC DIAGRAM<br />

THERMAL DATA<br />

Symbol Parameter Value Unit<br />

Rth j-case Thermal Resistance Junction-case Max. 3 °C/W<br />

2/20

<strong>TDA2005</strong><br />

BRIDGE AMPLIFIER APPLICATION (<strong>TDA2005</strong>M)<br />

Figure 1 : Test and Application Circuit (Bridge amplifier)<br />

Figure 2 : P.C. Board and Components Layout of Figure 1 (1:1 scale)<br />

3/20

<strong>TDA2005</strong><br />

ELECTRICAL CHARACTERISTICS (refer to the Bridge applicationcircuit, Tamb =25 o C, GV = 50dB,<br />

Rth (heatsink) =4 o C/W, unless otherwise specified)<br />

Symbol Parameter Test Conditions Min. Typ. Max. Unit<br />

V s Supply Voltage 8 18 V<br />

V os Output Offset Voltage (1)<br />

(between pin 8 and pin 10)<br />

V s = 14.4V<br />

V s = 13.2V<br />

Id Total Quiescent Drain Current V s = 14.4V R L =4Ω<br />

Vs= 13.2V RL = 3.2Ω<br />

P o Output Power d = 10% f = 1 Hz<br />

V s = 14.4V R L =4Ω<br />

R L = 3.2Ω<br />

V s = 13.2V R L = 3.2 Ω<br />

d Distortion f = 1kHz<br />

V s = 14.4V R L =4Ω<br />

P o = 50mW to 15W<br />

V s = 13.2V R L = 3.2Ω<br />

P o = 50mW to 13W<br />

V i Input Sensitivity f = 1kHz<br />

Po =2W RL =4Ω<br />

P o =2W R L = 3.2Ω<br />

R i Input Resistance f = 1kHz 70 kΩ<br />

f L Low Frequency Roll Off (– 3dB) R L = 3.2Ω 40 Hz<br />

f H High Frequency Roll Off (– 3dB) R L = 3.2Ω 20 kHz<br />

G v Closed Loop Voltage Gain f = 1kHz 50 dB<br />

e N Total Input Noise Voltage R g = 10kΩ (2) 3 10 µV<br />

SVR Supply Voltage Rejection R g = 10kΩ, C 4 =10µF<br />

f ripple = 100Hz, V ripple = 0.5V<br />

45 55 dB<br />

η Efficiency V s = 14.4V, f = 1 kHz<br />

P o = 20W R L =4Ω<br />

P o = 22W R L = 3.2Ω<br />

Vs = 13.2V, f = 1 kHz<br />

Po = 19W RL = 3.2Ω<br />

T j Thermal Shut-down Junction<br />

Temperature<br />

V OSH Output Voltage with one Side of<br />

Notes : 1. the For Speaker <strong>TDA2005</strong>M shorted only to ground<br />

2. Bandwith Filter :22Hz to 22kHz.<br />

V s = 14.4V, R L =4Ω<br />

f = 1kHz, P tot = 13W<br />

18<br />

20<br />

17<br />

75<br />

70<br />

20<br />

22<br />

19<br />

9<br />

8<br />

60<br />

60<br />

58<br />

150<br />

150<br />

150<br />

160<br />

1<br />

1<br />

mV<br />

mV<br />

mA<br />

mA<br />

W<br />

%<br />

%<br />

mV<br />

mV<br />

%<br />

%<br />

%<br />

145 °C<br />

V s = 14.4V R L =4Ω<br />

V s = 13.2V R L = 3.2Ω 2 V<br />

4/20

<strong>TDA2005</strong><br />

Figure 3 :<br />

Output Offset Voltage versus<br />

Supply Voltage<br />

Figure 4 :<br />

Distortion versus Output Power<br />

(bridge amplifier)<br />

Figure 5 :<br />

Distortion versus Output Power<br />

(bridge amplifier)<br />

BRIDGE AMPLIFIER DESIGN<br />

The following consideraions can be useful when designing a bridge amplifier.<br />

V omax<br />

I o max<br />

P omax<br />

Where :<br />

Parameter Single Ended Bridge<br />

Peak Output Voltage (before clipping)<br />

Peak Output Current (before clippling)<br />

RMS Output Power (before clipping)<br />

VCE sat = output transistors saturation voltage<br />

VS = allowable supply voltage<br />

RL = load impedance<br />

1<br />

2 (V s –2V CE sat ) V s –2V CE sat<br />

1 VS − 2V CE sat<br />

2 R L<br />

V S − 2V CE sat<br />

R L<br />

1 (V S − 2V CE sat ) 2 (V S −2V CE sat ) 2<br />

4 2R L 2R L<br />

5/20

<strong>TDA2005</strong><br />

Voltage and current swings are twice for a bridge<br />

amplifier in comparison with single endedamplifier.<br />

In order words, with the same RL the bridge configuration<br />

can deliver an output power that is four<br />

times the output power of a single ended amplifier,<br />

while, with the same max output current the bridge<br />

configuration can deliver an output power that is<br />

twice the output power of a single ended amplifier.<br />

Core must be taken when selecting VS and RL in<br />

order to avoid an output peak current above the<br />

absolute maximum rating.<br />

From the expression for IOmax, assuming VS<br />

= 14.4V and VCE sat = 2V, the minimum load that<br />

can be driven by <strong>TDA2005</strong> in bridge configuration<br />

is :<br />

RL min = V S − 2V CEsat<br />

I Omax<br />

=<br />

14.4 −4<br />

3.5<br />

= 2.97Ω<br />

The voltagegainof thebridge configurationisgiven<br />

by (see Figure 34) :<br />

G V = V 0 R 1<br />

=1+<br />

V 1<br />

⎛<br />

⎜<br />

⎝<br />

+ R 3<br />

R 2 ⋅R 4 ⎞ R 4<br />

R 2 +R ⎟⎠ 4<br />

Forsufficiently high gains (40 to 50dB) it is possible<br />

to put R2 =R4and R3 =2R1, simplifing the formula<br />

in :<br />

GV =4 R 1<br />

R 2<br />

G v (dB) R 1 (Ω) R 2 =R 4 (Ω) R 3 (Ω)<br />

40<br />

50<br />

1000<br />

1000<br />

39<br />

12<br />

Figure 6 : Bridge Configuration<br />

2000<br />

2000<br />

STEREO AMPLIFIER APPLICATION (<strong>TDA2005</strong>S)<br />

Figure 7 : Typical Application Circuit<br />

6/20

<strong>TDA2005</strong><br />

ELECTRICAL CHARACTERISTICS (refer to the Stereo application circuit, Tamb =25 o C, GV = 50dB,<br />

Rth (heatsink) =4 o C/W, unless otherwwise specified)<br />

Symbol Parameter Test Conditions Min. Typ. Max. Unit<br />

V s Supply Voltage 8 18 V<br />

V o Quiescent Output Voltage V s = 14.4V<br />

V s = 13.2V<br />

Id Total Quiescent Drain Current Vs = 14.4V<br />

V s = 13.2V<br />

P o Output Power (each channel) f = 1kHz, d = 10%<br />

V s = 14.4V R L =4Ω<br />

R L = 3.2Ω<br />

R L =2Ω<br />

R L = 1.6Ω<br />

V s = 13.2V R L = 3.2Ω<br />

R L = 1.6Ω<br />

V s = 16V R L =2Ω<br />

d Distortion (each channel) f = 1kHz<br />

V s = 14.4V R L =4Ω<br />

P o = 50mW to 4W<br />

V s = 14.4V R L =2Ω<br />

P o = 50mW to 6W<br />

V s = 13.2V R L = 3.2Ω<br />

Po = 50mW to 3W<br />

V s = 13.2V R L = 1.6Ω<br />

P o = 40mW to 6W<br />

CT Cross Talk (1) V s = 14.4V, V o =4V RMS<br />

R L =4Ω,R g =5kΩ<br />

f = 1kHz<br />

f = 10kHz<br />

V i Input Saturation Voltage 300 mV<br />

V i Input Sensitivity f = 1kHz, P o =1W<br />

RL=4Ω<br />

R L = 3.2Ω<br />

R i Input Resistance f = 1kHz 70 200 kΩ<br />

f L Low Frequency Roll Off (– 3dB) RL =2Ω 50 Hz<br />

f H High Frequency Roll Off (– 3dB) R L =2Ω 15 kHz<br />

G v Voltage Gain (open loop) f = 1kHz 90 dB<br />

G v Voltage Gain (closed loop) f = 1kHz 48 50 51 dB<br />

∆ G v Closed Loop Gain Matching 0.5 dB<br />

e N Total Input Noise Voltage R g = 10kΩ (2) 1.5 5 µV<br />

SVR Supply Voltage Rejection R g = 10kΩ, C 3 =10µF<br />

f ripple = 100Hz, V ripple = 0.5V<br />

35 45 dB<br />

η Efficiency V s = 14.4V, f = 1kHz<br />

P o = 6.5W R L =4Ω<br />

P o = 10W R L =2Ω<br />

Vs= 13.2V, f = 1kHz<br />

Po = 6.5W RL = 3.2Ω<br />

Po = 100W RL = 1.6Ω<br />

Notes : 1. For <strong>TDA2005</strong>M only<br />

2. Bandwith Filter :22Hz to 22kHz.<br />

6.6<br />

6<br />

6<br />

7<br />

9<br />

10<br />

6<br />

9<br />

7.2<br />

6.6<br />

65<br />

62<br />

6.5<br />

8<br />

10<br />

11<br />

6.5<br />

10<br />

12<br />

0.2<br />

0.3<br />

0.2<br />

0.3<br />

60<br />

45<br />

6<br />

5.5<br />

70<br />

60<br />

70<br />

60<br />

7.8<br />

7.2<br />

120<br />

120<br />

1<br />

1<br />

1<br />

1<br />

V<br />

V<br />

mA<br />

mA<br />

W<br />

%<br />

%<br />

%<br />

%<br />

dB<br />

mV<br />

%<br />

%<br />

%<br />

%<br />

7/20

<strong>TDA2005</strong><br />

Figure 8 :<br />

Quiescent Output Voltage versus<br />

Supply Voltage (Stereo amplifier)<br />

Figure 9 :<br />

Quiescent Drain Current versus<br />

Supply Voltage (Stereo amplifier)<br />

Figure 10 : Distortion versus Output Power<br />

(Stereo amplifier)<br />

Figure 11 : Output Power versus Supply Voltage<br />

(Stereo amplifier)<br />

Figure 12 : Output Power versus Supply Voltage<br />

(Stereo amplifier)<br />

Figure 13 : Distortion versus Frequency<br />

(Stereo amplifier)<br />

8/20

<strong>TDA2005</strong><br />

Figure 14 : Distortion versus Frequency<br />

(Stereo amplifier)<br />

Figure 15 : Supply Voltage Rejection versus C3<br />

(Stereo amplifier)<br />

Figure 16 : Supply Voltage Rejection versus<br />

Frequency (Stereo amplifier)<br />

Figure 17 : Supply Voltage Rejection versus<br />

C2 and C3 (Stereo amplifier)<br />

Figure 18 : Supply Voltage Rejection versus<br />

C2 and C3 (Stereo amplifier)<br />

Figure 19 : Gain versus Input Sensitivity<br />

(Stereo amplifier)<br />

9/20

<strong>TDA2005</strong><br />

Figure 20 : Gain versus Input Sensitivity<br />

(Stereo amplifier)<br />

Figure 21 : Total Power Dissipation and Efficiency<br />

versus Output Power<br />

(Bridge amplifier)<br />

Figure 22 : Total Power Dissipation and Efficiency<br />

versus Output Power<br />

(Stereo amplifier)<br />

10/20

<strong>TDA2005</strong><br />

APPLICATION SUGGESTION<br />

The recommended values of the components are those shown on Bridge applicatiion circuit of Figure 1.<br />

Different values can be used ; the following table can help the designer.<br />

Comp.<br />

Recom.<br />

Value<br />

Purpose Larger Than Smaller Than<br />

R 1 120 kΩ Optimization of the Output<br />

Symmetry<br />

Smaller P o max<br />

Smaller P o max<br />

R 2<br />

R3<br />

1kΩ<br />

2kΩ<br />

R 4 ,R 5 12 Ω Closed Loop Gain Setting (see<br />

Bridge Amplifier Design) (*)<br />

R6, R7 1Ω Frequency Stability Danger of Oscillation at High<br />

Frequency with Inductive Loads<br />

C 1 2.2 µF Input DC Decoupling<br />

C 2 2.2 µF Optimization of Turn on Pop and<br />

Turn on Delay<br />

High Turn on Delay<br />

Higher Turn on Pop, Higher<br />

Low Frequency Cut-off,<br />

Increase of Noise<br />

C 3 0.1 µF Supply by Pass Danger of Oscillation<br />

C4 10 µF Ripple Rejection Increase of SVR, Increase of<br />

the Switch-on Time<br />

Degradation of SVR.<br />

C 5 ,C 7 100 µF Bootstrapping Increase of Distortion<br />

at low Frequency<br />

C6, C8 220 µF Feedback Input DC Decoupling,<br />

Low Frequency Cut-off<br />

Higher Low Frequency<br />

Cut-off<br />

C 9 ,C 10 0.1 µF Frequency Stability Danger of Oscillation<br />

(*) The closed loop gain must be higher than 32dB.<br />

11/20

<strong>TDA2005</strong><br />

APPLICATION INFORMATION<br />

Figure 23 : Bridge Amplifier without Boostrap<br />

Figure 24 : P.C.Board and ComponentsLayout of Figure 23 (1:1 scale)<br />

12/20

<strong>TDA2005</strong><br />

APPLICATION INFORMATION (continued)<br />

Figure 25 : Low Cost Bridge Amplifier (G V = 42dB)<br />

Figure 26 : P.C.Board and ComponentsLayout of Figure 25 (1:1 scale)<br />

13/20

<strong>TDA2005</strong><br />

APPLICATION INFORMATION (continued)<br />

Figure 27 : 10 + 10 W Stereo Amplifier with Tone Balance and LoudnessControl<br />

Figure 28 : Tone Control Response<br />

(circuit of Figure 29)<br />

14/20

<strong>TDA2005</strong><br />

APPLICATION INFORMATION (continued)<br />

Figure 29 : 20W Bus Amplifier<br />

Figure 30 : Simple 20W Two Way Amplifier (FC = 2kHz)<br />

15/20

<strong>TDA2005</strong><br />

APPLICATION INFORMATION (continued)<br />

Figure 31 : Bridge Amplifier Circuit suited for Low-gain Applications (GV = 34dB)<br />

Figure 32 : Example of Muting Circuit<br />

16/20

<strong>TDA2005</strong><br />

BUILT-IN PROTECTION SYSTEMS<br />

Load Dump Voltage Surge<br />

The <strong>TDA2005</strong> has a circuit which enables it to<br />

withstanda voltagepulse train, on Pin 9, of the type<br />

shown in Figure 34.<br />

If the supply voltage peaks to more than 40V, then<br />

an LC filter must be inserted between the supply<br />

and pin 9, in order to assure that the pulses at pin<br />

9 will be held withing the limits shown.<br />

AsuggestedLC networkis shownin Figure33.With<br />

this network, a train of pulses with amplitude up to<br />

120V and width of 2ms can be applied at point A.<br />

This type of protection is ON when the supply<br />

voltage (pulse or DC) exceeds 18V.For this reason<br />

the maximum operating supply voltage is 18V.<br />

Figure 33<br />

Figure 34<br />

Open Ground<br />

When the ratio is in the ON condition and the<br />

ground is accidentally opened, a standard audio<br />

amplifier will be damaged.On the <strong>TDA2005</strong> protection<br />

diodes are included to avoid any damage.<br />

Inductive Load<br />

A protection diode is provided to allow use of the<br />

<strong>TDA2005</strong> with inductive loads.<br />

DC Voltage<br />

The maximum operating DC voltage for the<br />

<strong>TDA2005</strong> is 18V.<br />

However the device can withstand a DC voltageup<br />

to 28V with no damage. This could occur during<br />

winterif twobatteriesare seriesconnectedto crank<br />

the engine.<br />

Thermal Shut-down<br />

The presence of a thermallimiting circuit offers the<br />

following advantages :<br />

1) an overload on the output (even if it is<br />

permanent), or an excessive ambient<br />

temperature can be easily withstood.<br />

2) the heatsink can have a smaller factor of safety<br />

compared with that of a conventional circuit.<br />

There is no device damage in the case of<br />

excessive junction temperature : all that<br />

happensis thatPO (and thereforePtot) and Id are<br />

reduced.<br />

The maximum allowable power dissipation depends<br />

upon the size of the externalheatsink(i.e.its<br />

thermal resistance) ; Figure 35 shows the dissipable<br />

power as a function of ambient temperature for<br />

different thermal resistance.<br />

Loudspeaker Protection<br />

The circuit offers loudspeaker protection during<br />

short circuit for one wire to ground.<br />

Short Circuit (AC and DC conditions)<br />

The<strong>TDA2005</strong>can withstanda permanentshort-circuit<br />

on the output for a supply voltage up to 16V.<br />

Polarity Inversion<br />

High current (up to 10A) can be handled by the<br />

device with no damage for a longer period than the<br />

blow-out time of a quick 2A fuse (normally connected<br />

in series with the supply). This feature is<br />

added to avoid destruction, if during fitting to the<br />

car, a mistake on the connection of the supply is<br />

made.<br />

17/20

<strong>TDA2005</strong><br />

Figure 35 : Maximum Allowable Power Dissipation<br />

versus Ambient Temperature<br />

Figure 36 : Output Power and Drain Current versus<br />

Case Temperature<br />

Figure 37 : Output Power and Drain Current versus<br />

Case Temperature<br />

18/20

<strong>TDA2005</strong><br />

DIM.<br />

mm<br />

inch<br />

MIN. TYP. MAX. MIN. TYP. MAX.<br />

A 5 0.197<br />

B 2.65 0.104<br />

C 1.6 0.063<br />

D 1 0.039<br />

E 0.49 0.55 0.019 0.022<br />

F 0.88 0.95 0.035 0.037<br />

G 1.45 1.7 1.95 0.057 0.067 0.077<br />

G1 16.75 17 17.25 0.659 0.669 0.679<br />

H1 19.6 0.772<br />

H2 20.2 0.795<br />

L 21.9 22.2 22.5 0.862 0.874 0.886<br />

L1 21.7 22.1 22.5 0.854 0.87 0.886<br />

L2 17.4 18.1 0.685 0.713<br />

L3 17.25 17.5 17.75 0.679 0.689 0.699<br />

L4 10.3 10.7 10.9 0.406 0.421 0.429<br />

L7 2.65 2.9 0.104 0.114<br />

M 4.25 4.55 4.85 0.167 0.179 0.191<br />

M1 4.73 5.08 5.43 0.186 0.200 0.214<br />

S 1.9 2.6 0.075 0.102<br />

S1 1.9 2.6 0.075 0.102<br />

Dia1 3.65 3.85 0.144 0.152<br />

OUTLINE AND<br />

MECHANICAL DATA<br />

Multiwatt11 V<br />

19/20

<strong>TDA2005</strong><br />

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of<br />

use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted<br />

by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to<br />

change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not<br />

authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.<br />

The ST logo is a registered trademark of STMicroelectronics<br />

© 1998 STMicroelectronics – Printed in Italy – All Rights Reserved<br />

STMicroelectronics GROUP OF COMPANIES<br />

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands -<br />

Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.<br />

http://www.st.com<br />

20/20